# Contents

| reface to the Seventh Edition (SIE)             | XI |

|-------------------------------------------------|----|

| reface                                          | xv |

| 1. Digital Principles                           | 1  |

| 1.1 Definitions for Digital Signals 2           |    |

| 1.2 Digital Waveforms 4                         |    |

| 1.3 Digital Logic 8                             |    |

| 1.4 Moving and Storing Digital Information 13   |    |

| 1.5 Digital Operations 17                       |    |

| 1.6 Digital Computers 22                        |    |

| 1.7 Digital Integrated Circuits 26              |    |

| 1.8 Digital IC Signal Levels 32                 |    |

| Summary 35                                      |    |

| Glossary 35                                     |    |

| Problems 36                                     |    |

| 2. Digital Logic                                | 40 |

| 2.1 The Basic Gates—NOT, OR, AND 40             |    |

| 2.2 Universal Logic Gates—NOR, NAND 48          |    |

| 2.3 AND-OR-Invert Gates 57                      |    |

| 2.4 Positive and Negative Logic 59              |    |

| 2.5 Introduction to HDL 61                      |    |

| Summary 68                                      |    |

| Glossary 69                                     |    |

| Problems 69                                     |    |

| Laboratory Experiment 73                        |    |

| 3 Combinational Logic Circuits                  | 74 |

| 3.1 Boolean Laws and Theorems 75                |    |

| 3.2 Sum-of-Products Method 81                   |    |

| 3.3 Truth Table to Karnaugh Map 84              |    |

| 3.4 Pairs, Quads, and Octets 86                 |    |

| 3.5 Karnaugh Simplifications 89                 |    |

| 3.6 Don't-care Conditions 93                    |    |

| 3.7 Product-of-sums Method 95                   |    |

| 3.8 Product-of-sums Simplification 98           |    |

| 3.9 Simplification by Quine-McClusky Method 102 |    |

|        | Contents                                              |

|--------|-------------------------------------------------------|

|        | \                                                     |

| 3.10   | Hazards and Hazard Covers 104                         |

| 3/11   | HDL Implementation Models 108                         |

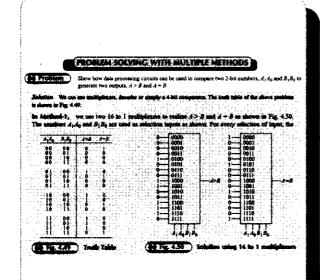

|        | Problem Solving with Multiple Methods 110             |

|        | Summary 111                                           |

|        | Glossary 112                                          |

|        | Problems 112                                          |

| 4 Doto | Laboratory Experiment 116 -Processing Circuits        |

|        | •                                                     |

|        | Multiplexers 118                                      |

|        | Demultiplexers 127 1-of-16 Decoder 130                |

|        | BCD-to-decimal Decoders 133                           |

|        | Seven-segment Decoders 136                            |

|        | Encoders 138                                          |

|        | Exclusive-OR Gates 141                                |

|        | Parity Generators and Checkers 143                    |

|        | Magnitude Comparato, 146                              |

|        | Read-only Memory 148                                  |

|        | Programmable Array Logic 154                          |

|        | Programmable Logic Arrays 156                         |

|        | Troubleshooting with a Logic Probe 158                |

|        | *****                                                 |

| 7,17   |                                                       |

|        | Problem Solving with Multiple Methods 161 Summary 163 |

|        | Glossary 163                                          |

|        | Problems 164                                          |

|        | Laboratory Experiment 169                             |

| 5. Num | ber Systems and Codes                                 |

|        | Binary Number System 171                              |

| 5.2    | Binary-to-decimal Conversion 173                      |

| 5.3    | Decimal-to-binary Conversion 176                      |

| 5.4    | Octal Numbers 179                                     |

| 5.5    | Hexadecimal Numbers 183                               |

| 5.6    | The ASCII Code 190                                    |

| 5.7    | The Excess-3 Code 192                                 |

| 5.8    | The Gray Code 193                                     |

| 5.9    | Troubleshooting with a Logic Pulser 194               |

| 5.10   | Error Detection and Correction 196                    |

|        | Problem Solving with Multiple Methods 198             |

|        | Summary 199                                           |

|        | Glossary 200                                          |

|        | Problems 200                                          |

Laboratory Experiment 205

| 6. | Arith  | metic Circuits                         |     | 206 |

|----|--------|----------------------------------------|-----|-----|

|    | 6.1    | Binary Addition 207                    |     |     |

|    | 6.2    | Binary Subtraction 211                 |     |     |

|    | 6.3    | Unsigned Binary Numbers 212            |     |     |

|    | 6.4    | Sign-magnitude Numbers 214             |     |     |

|    | 6.5    | 2's Complement Representation 216      |     |     |

|    | 6.6    | 2's Complement Arithmetic 220          |     |     |

|    | 6.7    | Arithmetic Building Blocks 226         |     |     |

|    | 6.8    | The Adder-subtracter 228               |     |     |

|    | 6.9    | Fast Adder 232                         |     |     |

|    | 6.10   | Arithmetic Logic Unit 235              |     |     |

|    | 6.11   | Binary Multiplication and Division 237 |     |     |

|    | 6.12   | Arithmetic Circuits Using HDL 237      |     |     |

|    |        | Problem Solving with Multiple Methods  | 239 |     |

|    |        | Summary 240                            |     |     |

|    |        | Glossary 241                           |     |     |

|    |        | Problems 241                           |     |     |

| _  |        | Laboratory Experiment 243              |     | 244 |

| 7. |        | s and Timing Circuits                  |     | 244 |

|    |        | Clock Waveforms 244                    |     |     |

|    |        | TTL Clock 249                          |     |     |

|    |        | Schmitt Trigger 250                    |     |     |

|    |        | 555 Timer—Astable 253                  |     |     |

|    |        | 555 Timer—Monostable 256               |     |     |

|    |        | Monostables with Input Logic 258       |     |     |

|    | 7.7    | Pulse-forming Circuits 262             |     |     |

|    |        | Problem Solving with Multiple Methods  | 264 |     |

|    |        | Summary 265                            |     |     |

|    |        | Glossary 266                           |     |     |

|    |        | Problems 266 Laboratory Experiment 268 |     |     |

| Q  | Flip-l |                                        |     | 270 |

| υ. |        | RS FLIP-FLOPs 271                      |     |     |

|    |        | Gated FLIP-FLOPs 276                   |     |     |

|    |        | Edge-triggered RS FLIP-FLOPs 279       |     |     |

|    |        | Edge-triggered D FLIP-FLOPs 281        |     |     |

|    |        | Edge-triggered JK FLIP-FLOPs 283       |     |     |

|    |        | FLIP-FLOP Timing 285                   |     |     |

|    |        | Edge Triggering through Input Lock Out | 286 |     |

|    |        | /K Master-slave FLIP-FLOPs 288         |     |     |

|    |        | Switch Contact Bounce Circuits 289     |     |     |

|    |        | Various Representations of FLIP-FLOPs  | 290 |     |

|    |        | Analysis of Sequential Circuits 293    |     |     |

|    |        | <b>1</b>                               |     |     |

|    |        |                                        |     |     |

|     | 8.12   | Conversion of FLIP-FLOPs: A Synthesis Example 296     |     |

|-----|--------|-------------------------------------------------------|-----|

|     | 8.13   | HDL Implementation of FLIP-FLOP 298                   |     |

|     |        | Problem Solving with Multiple Methods 301             |     |

|     |        | Summary 303                                           |     |

|     |        | Glossary 303                                          |     |

|     |        | Problems 304                                          |     |

|     |        | Laboratory Experiment 306                             |     |

| 9,  | Regis  | sters                                                 | 308 |

|     | 9.1    | Types of Registers 309                                |     |

|     | 9.2    | Serial In–serial Out 310                              |     |

|     | 9.3    | Serial In–parallel Out 313                            |     |

|     | 9.4    | Parallel In-serial Out 316                            |     |

|     | 9.5    | Parallel In–parallel Out 320                          |     |

|     |        | Universal Shift Register 324                          |     |

|     |        | Applications of Shift Registers 325                   |     |

|     |        | Register Implementation in HDL 333                    |     |

|     |        | Problem Solving with Multiple Methods 334             |     |

|     |        | Summary 335                                           |     |

|     |        | Glossary 336                                          |     |

|     |        | Problems 336                                          |     |

|     |        | Laboratory Experiment 339                             |     |

| 10. | Coun   | ters                                                  | 341 |

|     | 10.1   | Asynchronous Counters 342                             |     |

|     | 10.2   | Decoding Gates 346                                    |     |

|     |        | Synchronous Counters 349                              |     |

|     |        | Changing the Counter Modulus 357                      |     |

|     | 10.5   | Decade Counters 363                                   |     |

|     | 10.6   | Presettable Counters 368                              |     |

|     | 10.7   | Counter Design as a Synthesis Problem 376             |     |

|     |        | A Digital Clock 381                                   |     |

|     | 10.9   | Counter Design using HDL 384                          |     |

|     |        | Problem Solving with Multiple Methods 386             |     |

|     |        | Summary 387                                           |     |

|     |        | Glossary 388                                          |     |

|     |        | Problems 388                                          |     |

|     |        | Laboratory Experiment 390                             |     |

| 11. | Design | n of Synchronous and Asynchronous Sequential Circuits | 392 |

|     | PART   | A: Design of Synchronous Sequential Circuit 393       |     |

|     |        | Model Selection 393                                   |     |

|     | 11.2   | State Transition Diagram 394                          |     |

|     |        | State Synthesis Table 396                             |     |

|     |        | Design Equations and Circuit Diagram 398              |     |

|     |        | Implementation using Read Only Memory 400             |     |

|     |        |                                                       |     |

|     |       |                                                    | _   |

|-----|-------|----------------------------------------------------|-----|

|     |       | Algorithmic State Machine 404                      | ٠   |

|     |       | State Reduction Technique 409                      |     |

|     |       | <b>F B</b> : Asynchronous Sequential Circuit 413   |     |

|     |       | Analysis of Asynchronous Sequential Circuit 414    |     |

|     |       | Problems with Asynchronous Sequential Circuits 417 |     |

|     |       | Design of Asynchronous Sequential Circuit 419      |     |

|     | 11.11 | FSM Implementation in HDL 423                      |     |

|     |       | Problem Solving with Multiple Methods 425          |     |

|     |       | Summary 432                                        |     |

|     |       | Glossary 432<br>Problems 433                       |     |

|     |       | Laboratory Experiment 435                          |     |

| 12  | D/A ( | Coversion and A/D Conversion                       | 438 |

| 12. |       | Variable, Resistor Networks 439                    | 436 |

|     |       | Binary Ladders 442                                 |     |

|     |       | D/A Converters 447                                 |     |

|     |       | D/A Accuracy and Resolution 454                    |     |

|     |       | A/D Converter—Simultaneous Conversion 455          |     |

|     |       | A/D Converter—Counter Method 458                   |     |

|     |       | Continuous A/D Conversion 461                      |     |

|     |       | A/D Techniques 464                                 |     |

|     |       | Dual-slope A/D Conversion 467                      |     |

|     |       | A/D Accuracy and Resolution 471                    |     |

|     |       | Summary 472                                        |     |

|     |       | Glossary 473                                       |     |

|     |       | Problems 473                                       |     |

| 13. | Mem   | ory                                                | 476 |

|     | 13.1  | Basic Terms and Ideas 477                          |     |

|     | 13.2  | Magnetic Memory 479                                |     |

|     | 13.3  | Optical Memory 483                                 |     |

|     | 13.4  | Memory Addressing 486                              |     |

|     |       | ROMs, PROMs, and EPROMs 491                        |     |

|     |       | RAMs 496                                           |     |

|     |       | Sequential Programmable Logic Devices 503          |     |

|     | 13.8  | Content Addressable Memory 506                     |     |

|     |       | Summary 507                                        |     |

|     |       | Glossary 508                                       |     |

| 1.4 | Th: " | Problems 509                                       |     |

| 14. | _     | al Integrated Circuits                             | 512 |

|     |       | Switching Circuits 513                             |     |

|     |       | 7400 TTL 518 TTL Proposition 520                   |     |

|     | 14.5  | TTL Parameters 520                                 |     |

| Λ. | _1_ | 1 |  |

|----|-----|---|--|

|    | nto |   |  |

14.4 TTL Overview 528

| 14.5 Open-collector Gates 530                                                  |            |

|--------------------------------------------------------------------------------|------------|

| 14.6 Three-state TTL Devices 532                                               |            |

| 14.7 External Drive for TTL Loads 534                                          |            |

| 14.8 TTL Driving External Loads 537                                            |            |

| 14.9 74C00 CMOS 538                                                            |            |

| 14.10 CMOS Characteristics 541                                                 |            |

| 14.11 TTL-to-CMOS Interface 544                                                |            |

| 14.12 CMOS-to-TTL Interface 546                                                |            |

| 14.13 Current Tracers 548                                                      |            |

| Summary 550                                                                    |            |

| Glossary 551                                                                   |            |

| Problems 552                                                                   | ***        |

| 15. Applications                                                               | 558        |

| 15.1 Multiplexing Displays 559                                                 |            |

| 15.2 Frequency Counters 565                                                    |            |

| 15.3 Time Measurement 570                                                      |            |

| 15.4 Using the ADC0804 571 15.5 Microprocessor-compatible A/D Converters 577   |            |

| 15.5 Microprocessor-compatible A/D Converters 577  15.6 Digital Voltmeters 585 |            |

| Summary 591                                                                    |            |

| Problems 591                                                                   |            |

| 16. A Simple Computer Design                                                   | 593        |

| 16.1 Building Blocks 594                                                       | <b>272</b> |

| 16.2 Register Transfer Language 597                                            |            |

| 16.3 Execution of Instructions, Macro and Micro Operations 599                 |            |

| 16.4 Design of Control Unit 602                                                |            |

| 16.5 Programming Computer 605                                                  |            |

| Summary 612                                                                    |            |

| Glossary 612                                                                   |            |

| Problems 613                                                                   |            |

| Appendix 1: Binary-Hexadecimal-Decimal Equivalents 615                         |            |

| Appendix 2: 2's Complement Representation 621                                  |            |

| Appendix 3: TTL Devices 625                                                    |            |

| Appendix 4: CMOS Devices 628                                                   |            |

| Appendix 5: Codes 630                                                          |            |

| Appendix 6: BCD Codes 633                                                      |            |

| Appendix 7: Overview of IEEE Std. 91-1984, Explanation of Logic Symbols        | 638        |

| Appendix 8: Pinout Diagrams 643                                                |            |

| Appendix 9: Answers to Selected Odd-Numbered Problems 647                      |            |

| Index                                                                          | 672        |

|                                                                                | J. 2       |

# Preface to the Seventh Edition (SIE)

The seventh edition of Digital Principles and Applications continues with the upgradation of the work started in its previous edition. The job was to build upon the strengths of one of the best introductory and authentic texts in the field of Digital Electronics—its lucid language, down-to-earth approach, detailed analysis and ready-to-use information for laboratory practices. The sixth edition sought improvement primarily by (i) strengthening the design or synthesis aspect that included advanced material, such as a simple computer design, and (ii) incorporating many new topics like Hardware Description Language, Asynchronous Sequential Circuit, Algorithm State Machine chart, Quine-McClusky algorithm, Look Ahead Carry Adder, etc.

The tremendous response to the improvements made in the sixth edition from the academic community prompted us to work on their suggestions and come out with this seventh edition.

### **NEW TO THIS EDITION**

The seventh edition has been revised extensively and restructured to emphasize new and important concepts in Digital Principles and Applications. This edition increases the depth and breadth of the title by incorporating latest information on existing topics like Boolean Algebra, Schmitt Trigger, 555 Timer, Edge Triggering, Memory Cell, Computer Architecture, and also introduces new topics like Noise Margin, Error Detection and Correction, Universal Shift Register and Content Addressable Memory.

The most notable change in this edition is the inclusion of two completely new features—problem solving by multiple methods and laboratory experiments—that will enable the student community develop deeper understanding of the application side of digital principles. Problem solving by multiple methods help students in understanding and appreciating different alternatives to reach a solution, without feeling stuck at any point of time. Laboratory experiments facilitate experimentation with different analysis and synthesis problems using digital integrated circuits (IC). Each experiment describes its aim, a short reference to theory, apparatus required and different work elements.

### THE BASIC FEATURES

The new edition retains its appeal as a complete self-study guide for a first-level course on Digital Logic and Digital Circuits. It will serve the purpose of a textbook for undergraduate students of CSE, ECE, EEE, Electronics and Instrumentation and IT. It will also be a valuable reference for students of MCA, BCA, DOEACC 'A' Level, as well as BSc/MSc (Computer Science/IT).

### The key features are:

- > Presence of various applications and lab experiments considering the common digital circuit design employed in industries (e.g., LCD display and ADC0804 operation).

- ➤ In-depth coverage of important topics like clock and timing circuits, D/A-A/D conversion, register, counters and memory.

- > Tutorial-based approach with section-end self test questions and problem solving through various methods.

- Useful discussion on TTL and CMOS devices and pin diagrams

- > Rich Pedagogy

- 180 Solved Examples

- · 290 Section-end Problems

- 500 Chapter-end Problems

### **COMPREHENSIVE WEBSITE**

An important addition to this title is the accompanying website—http://www.mhhe.com/leach/dpa7, designed to be an exhaustive Online Learning Centre (OLC). This website contains the following:

### For Students

- · Downloadable codes for HDL examples in the book

- Supplementary Reading material

Besides Quine-McClusky code and HDL examples, additional information and discussion on various supplementary materials like five-variable Karnaugh Map and Petrick's Algorithm will be available here. Regular updates on different topics of Digital Electronics will be posted to keep the reader informed about recent changes in this field.

### For Instructors

Instructors who have adopted this textbook can access a password-protected section that offers the following resources.

- · Solution manual

- · Chapterwise PowerPoint slides with diagrams and notes

### **ACKNOWLEDGEMENTS**

I would like to acknowledge the inspiration and support I received from Prof. B N Chatterji (Retd.), Prof. R N Pal (Retd.), Prof. R V Rajakumar, Prof. A Chakraborty, Prof. P P Chakraborty, Prof. D Datta, Prof. S Bannerjee, Prof. P K Biswas, Prof. S S Pathak, Prof. S Mukhopadhyaya, Prof. A S Dhar, Prof. I Chakraborty, Prof. P Mandal, Prof. S Mahapatra, Prof. T K Bhattacharya, and all my faculty colleagues at Indian Institute of Technology (IIT) Kharagapur, especially, from the Department of Electronics and Electrical Communication Engineering and G S Sanyal School of Telecommunications. But for the paucity of space, I would have named many others.

Thanks are due to my research students—Mr S Ari, Mr Md Sahidullah, Mr Israj Ali, and Mr A Mandal for their contribution at different stages of development of the edition. I acknowledge the benefit derived from my interaction with different batches of students while teaching the Digital Electronics subject—three years at Institute of Engineering and Management, Kolkata and over six years at IIT Kharagpur.

I am grateful to the esteemed reviewers for their encouraging comments and valuable suggestions for this edition.

### Sunil Mathur

Maharaja Agrasen Institute of Technology, New Delhi

### V Kumar

Maharaja Surajmal Institute of Technology, New Delhi

### Bijoy Bandopadhyay

University College of Science & Technology, Kolkata

### Anita Kanavalli

MS Ramaiah Institute of Technology, Bangalore

I also thank the entire team of Tata McGraw Hill Education, more specifically Vibha Mahajan, Shalini Jha, Ashes Saha, Surbhi Suman, Anjali Razdan and Baldev Raj for their support.

At this point, I humbly remember all my teachers and my father (late) G N Saha who provided me a great learning environment. I also fondly recollect the contributions in my upbringing of Kharagpur Vivekananda Yuva Mahamandal, Vivekananda Study Circle, IIT Kharagpur Campus and Ramakrishna Mission. I must mention the support I always received from my family—my mother, my parents-in-law, my sisters (specially Chhordi), Chhoto Jamaibabu, and last but not the least, my wife, Sanghita, and daughter, Upasana. The effort behind this work was mine but the time was all theirs.

GOUTAM SAHA

### **Feedback**

Due care has been taken to avoid any mistake in the print edition as well as in the OLC. However, any note on oversight as well as suggestions for further improvement sent at <a href="mailto:tmh.csefeedback@gmail.com">tmh.csefeedback@gmail.com</a> will be gratefully acknowledged (kindly mention the title and author name in the subject line). Also, please report to us any piracy of the book spotted by you.

# **Preface**

### **PURPOSE**

The fifth edition of Digital Principles and Applications is completely recorgnized. It is written for the individual who wishes to learn the principles of digital circuits and then apply them to useful, meaningful design. Thus the title. The material in this book is appropriate for an introductory course in digital logic in either a computer or an electronics program. It is also appropriate for "self-study" and as a "reference" for individuals working in the field. Emphasis is given to the two most popular digital circuit (IC) families—transistor-transistor logic (TTL) and complementary metal oxide silicon (CMOS) logic. Many of these individual ICs are discussed in detail, and pinouts for more than 60 digital IC chips are summarized in Appendix 8. Standard logic symbols are used along with the new IEEE standard logic. A review of the new IEEE symbols is given in the appendix.

### **BACKGROUND**

It is not necessary to have a background in electronics to study this text. A familiarity with Ohm's law and voltage and current in simple dc resistive circuits is helpful but not required. If you have no desire to learn about electronics, you can skip Chap. 13. To the extent possible, the remaining chapters are written to be independent of this material. If you have not studied electronics, Chap. 13 will provided the necessary background for you to converse successfully with those who have. Study it any time after Chap. 1. For "old-times" who have studied electronics, Chap. 13 will provide a good review and perhaps a new and valuable point of view. In any case, the material in Chap. 13 will certainly enhance both the knowledge and ability of anyone!

### **ORGANIZATION**

Each chapter begins with a contents that lists the subjects in each section. The contents listing is followed by a list of chapter objectives. At the end of each chapter section are review questions, called self-tests, which are intended to be a self-check of key ideas and concepts. At the end of each chapter, answers are supplied for the self-tests. A summary and a glossary are provided at the end of each chapter. In any subject area, there are many terms and concepts to be learned. The summary and glossary will provide you with the opportunity to be sure that you understand the *exact* meaning of these terms, phrases, and abbreviations, The end-of-chapter problems are arranged according to chapter sections. The problems reinforce ideas and concepts presented and allow you to apply them on your own. Solu-

tions to selected odd-numbered problems are given at the end of the book. In addition, the appendix contains reference material that will be useful from time to time.

### LABORATORY EXPERIMENTS

A complete set of experiments keyed to this text is available in a laboratory manual, Experiments for Digital Principles.

DONALD P. LEACH ALBERT PAUL MALVINO

# Visual Walkthrough

### OBJECTIVES

- state reduction techniques

Analysis of asynchronous sequential circuit

Problems specific to asynchronous sequential circuit

Design issues related to asynchronous sequential circuit

Design problem normally starts with a word description of input output relation and ends with a circuit diagram having sequential and combinatorial logic elements. The word description is first converted to a state transition diagram or Algorithmic State Machine (ASM) chart followed by preparation of state synthesis table. For filip-flop based implementation, excitation tables are used to generate design equations through Karnaugh Map. The final circuit diagram is developed from these design equations. In Read Only Memory (ROM) based implementation, excitation tables are not required nowever, flip-flops are used as delay elements. In this chapter, we show how these techniques can be used in sequential curcuit design.

There are two different approaches of state machine design called Moore model and Mealy model. In Moore model circuit diviny outputs or generated soilely from secondary outputs or memory values. In Mealy model circuit inputs, also known as primary inputs combine with memory elements to generate circuit output. Both the methods are discussed in detail in this chapter.

In general, sequential logic circuit design refers to synchronous clock-triggered circuit because of its design and implementation advantages. But there is increasing attention to asynchronous sequential logic

Every chapter opens with a set of chapter ob-

Benefits: These provide a quick look into the concepts that will be discussed in the chapter.

Every chapter contains several worked out examples totalling to 180 in the book.

Benefits: These will guide the students while understanding the concepts and working out the exercise problems.

## 4.14 HOL SMPLEMENTATION OF DATA PROCESSING CIRCUITS

This statement does following assignment. If, S=1, X=A and if S=0, X=B. One can use this state or the logic equation to realize a 2 to 1 multiplexer shown in Fig. 4.2(a) in one of the following ways.

module mux2tal(A,D0,D1,Y1) module mux2tal(A,D0,D1,Y1)

input A,D0,D1 '\* Circuit shown in Fig. 4-3(a) "/ circuit shown in Fig. 4-3(a) "/ output Y;

evaluation Y-(-A5D0)][X6D1];

evaluation Y-(-A5D0)][X6D1];

exaction and module discovered in Fig. 4-3 D1 : D0; /\*Conditional existingment\*/

The behavioral model can be used to describe the 2 to 1 multiplexers in following two different ways, one using it ... else statement and the other using case statement. The case evaluates an expression or a variable that can have multiple values each one corresponding to one statement in the following block. Depending on value of the expression, one of those statements get executed. The behavioral model of 2 to 1 multiplexer in both is given below:

make the number of the number

New to this edition, HDL, an interesting development in the field of hardware design, has been introduced.

Benefits: The relevant HDL description and codes are weaved into chapters to help students implement and design digital circuits.

### Programming a PAL

A PAL is different from a PROM because it has a programmable AND array and a fixed OR array. For instance, Fig. 4.43 shows a PAL with 4 inputs and 4 outputs. The x's on the input side are fixed locks, while the solid black bullets on the output side are fixed connections. With a PROM programmer, we can burn in the desired fundamental products, which are then ORed by the fixed output connections.

Fig. 4.43 Structure of PAL

Figures are used exhaustively in the text.

Benefits: These illustrate the concepts and methods described for better understanding.

### (PASELE-TEST)

- Analog signals are (continuous, discrete).

- Analog signals are (continuous, discrete).

The operation of a digited circuit is generally considered to be nonlinear. (T or F)

Write the beauty number for the docimal number 7.

Ac a tain digital circuit is designed to operate with voltage levels of -0.2 Vdc and -3.0 Vdc. if H = 1 = -0.2 Vdc and L = 0 = -3.0 Vdc, is the positive logic or negative logic?

Refer to Fig. 1.4c and describe the mesaging of the terms V<sub>cottage</sub> and V<sub>cottage</sub>.

Can V<sub>c</sub> over have a value within the forbidder band in Fig. 1.4c? Explain.

In Fig. 1.8c, H = +5.0 Vdc and L = +1.0 Vdc. What are the voltage levels between which the rise and fall times are measured?

- In Fig. 1.5a, H = +5.0 Vdc and L = +1.0 Vdc. What are the voltage levele between which the rise and full times are measured?

What is the value of Dux yoch M if the waveform in Fig. 1.6b is high for 2 ms and low for 5 ms?

Refer only to the visue of Low your penhod in Fig. 1.9c und determine the State of V if both G and V are low. Chack your response with the sent bable in Fig. 1.15c. Repeat if both G and V are high.

Refer only to the inverting vistate buffer symbol in Fig. 1.11c and determine the state of V if both G and V are high.

Refer only to the inverting vistate buffer symbol in Fig. 1.11c and determine the state of V if both G and V are high.

Por the AND gate in Fig. 1.13c, V = M and V = L. What is the state of V: 1.11c. Repost if both G and be are the value of V in the state of V if the North Y in the state of V: 1.11c. The dist is the state of V: 1.11c. The dist is the value of the value of V: 1.11c. The dist is the value of the value of V: 1.11c. The dist is the value of the value of V: 1.11c. The dist is the value of V: 1.11c. The dist is V in the value of V: 1.11c. The dist is V in the value of V: 1.11c. The dist is V in the value of V: 1.11c. The value of

A section called Self-Test appears after every section in every chapter.

Benefits: This will help students check their understanding of the concepts discussed in a section before moving on to the next section. Answers to Self-Tests are given at the end of that chapter.

A Brief summary is provided at the end of the chapters.

Benefits: Summary gives the essence of each chapter in brief and will be helpful for a quick review during the examinations.

### SUMMARY

2.43 shows there are of equivalent game. Changing from one to the other is accomplic disking bubbles, and changing AND is OR or OR to AND. Duringthe gate land NAN to Bustnets De Mongain's Birst and swoods Reprinters.

### Glossary

A glossary containing the important definitions and abbreviations is listed at the end of each chapter.

Benefits: It helps in memorising the important terms discussed in the chapter.

### GLOSSARY

- ALU Arithmetic logic unit.

\*\*anday signal A signal whose amplitude can take any value between given limits. A continuous signal.

\*\*binsay namabar A number code that uses only the digits 0 and 1 to represent quantities.

\*\*binsay have A number code that uses only the digits 0 and 1 to represent quantities.

\*\*binsay have a number code that uses only the digits 0 and 1 to represent quantities.

\*\*binsay have two types of charge carriers; a bipolat transition is any not put.

\*\*binsay digit.\*\*

\*\*binsay digit.\*\*

\*\*biffer A digital circuit capable of maintaining a required logic level white acting as a current source or a current sink for a given load.

\*\*chip A small pince of semiconductor on which an IC is formed.

\*\*CMOS Complementary metal-oxide stilicon.

An IC using both n-channel and p-channel field-effect transitions (FETS).

\*\*CPU Central processing unit.\*\*

\*\*CPT Cathod-ray tube.\*\*

\*\*clack A periodic, roctangular waveform used as a basic timing signal.\*\*

\*\*consuper a dispital circuit distigned to keep track of (to count) a number of events.

\*\*consuper a digital circuit distigned to change a digital number into another form.

\*\*demandisplexer\*\* (DEMUX) A digital circuit that will select only one of many invots.

- digital signal A signal whose amplitude can have only given discrete values between defined limits A signal that changes amplitude in discrete steps.

DIP Dual-indee package.

DIP Dual-indee package.

DIM Direct memory access.

DIM Direct memory access.

DIM procke for a periodic digital signal, the ratio of high level time to the period or the ratio of low level time to the period.

ECL Emitter-coupled logic.

encoder A unit designed to change a given signal into a digital jumber?

Alp-phop An electronic circuit that can store one bit of a binary number.

Jepsy dark A magnetically coated disk used to store digital data.

giver A digital circuit having two or more

- store digital data.

gent A digital circuit having two or more

imputs and a single output.

\*\*Anadomating A "request" to transfer data

into or out of a computer, followed by an

"acknowledge" signal, allowing data transfer

to begin.

- "acknowledge" signal, allowing data transfer to begin.

\*\*\* If Clitegrated circuit.

\*\*\* If Clitegrated A digital circuit, a twitching circuit, or any kind of two-state circuit that duplicates mental processes.

\*\*\* LST Large-scale integration.

\*\*\* amoney\*\* The area of a digital computer used in store moreans and disa.

### PROBLEMS

- 8.1 List as many bistable devices as you can think of—either electrical or mechanical. (Hint: Magnets, lamps, relays, etc.)

8.2 Rechaw the NOR-gast fip-flop in Fig. 8.3b and label the logic level on each pas for R = S = 0. Repeat for R = S = 1, for R = G and S = 1, and G = R = 1 and S = 0.

- and tabel the NAND-gate flip-flop in Fig. 8.7a and tabel the logic level on each pin for  $\overline{R} = \overline{S} = 0$ . Repeat for  $\overline{R} = \overline{S} = 1$ , for  $\overline{R} = 1$ , and  $\overline{S} = 0$ , and for  $\overline{R} = 0$  and  $\overline{S} = 1$ .

- 8.4 Redraw the NAND-gate flip-flop in Fig. 8.8 and label the logic level on each pin for R = S = 0. Repeat for R = S = 1, for R = 0 and S = 1, and for R = 1 and S = 0.

### Section 8.7

- 8.5 The waveforms in Fig. 8.50 drive the clocked RS flip-flop in Fig. 8.11. The clock signal goes from low to high at points A, C, E, and G. If Q is low before point A in time:

a. At what point does Q become a 1?

b. When does Q reset to 0?

### 64 Fg. 3.50

- 8.6 Use the information in the preceding problem and draw the waveform at Q.

8.7 Prove that the flip-flop realizations in Fig. 8.12 are equivalent by writing the logic level

8.8 The waveforms in Fig. 8.51 drive a D latch as shown in Fig. 8.15. What is the value of D stored in the flip-flop after the clock pulse is

- What is the advantage offered by an edge-triggered RS filp-floop over a clocked or gated RS filp-floop. The vertex of the the typical operation of an edge-triggered RS filp-floop. This circuit was connected in the laboratory, but the R and S inputs were mistalenly reversed. Draw the resulting waveform for Q.

An edge-triggered RS filp-floo will be used to produce the waveform Q with respect to the clock as shown in Fig. 8.52a. First, would you use a positive-edge- or a negative-edge-triggered filp-floop? Why? Draw the waveforms necessary at R and S to produce Q.

The text contains more than 250 section-end practice problems.

Benefits: These will help the students in improving their problem-solving skills.

## Multiple Methods

Each chapter contains numerous problems solved using multiple methods.

Benefits: Problem solving by multiple methods helps students in understanding and appreciating different alternatives to reach a solution, without feeling stuck at any point of time.

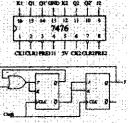

## abassian Exterimente

Each chapter contains a lab experiment.

Benefits: Laboratory experiments facilitate experimentation with different analysis and synthesis problems using digital integrated circuits (IC). These give a hands-on experience to the reader.

### LABORATORY EXPERIMENT

Able: The size of this superiment is to study D fip-flop and JK flip-flop and no them for

Theory: The truth ublic of D Rip-Bop an IK flip-flow are as follows.

Their characteristic equations is

IK Shy Stop: Q ... - JQ + K'Q.

Apparatus: 5 VDC Power supply, Multiposter, Bread Boerd, Clock Generator, and Oscilissospe:

Work element: 1C 7474 is a deal, edgeclacked, D flip-flop with both PRESET and CLEAR, input while 7476 is a deal, edgeclacked, M flip-flop data too, has both PRE-SET and CLEAR legat. Verify the resh table of the 1474 and 1475. When it is in making